Jaden aplikasyon

1. High-vitès sikwi entegre

2. Mikwo ond aparèy

3. Segondè sikwi entegre tanperati

4. Aparèy pouvwa

5. Ba pouvwa sikwi entegre

6. MEMS

7. Low vòltaj entegre kous

| Atik | Agiman | |

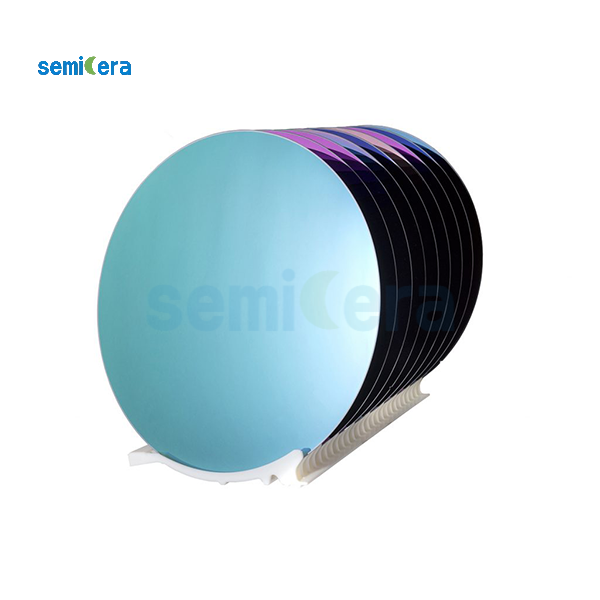

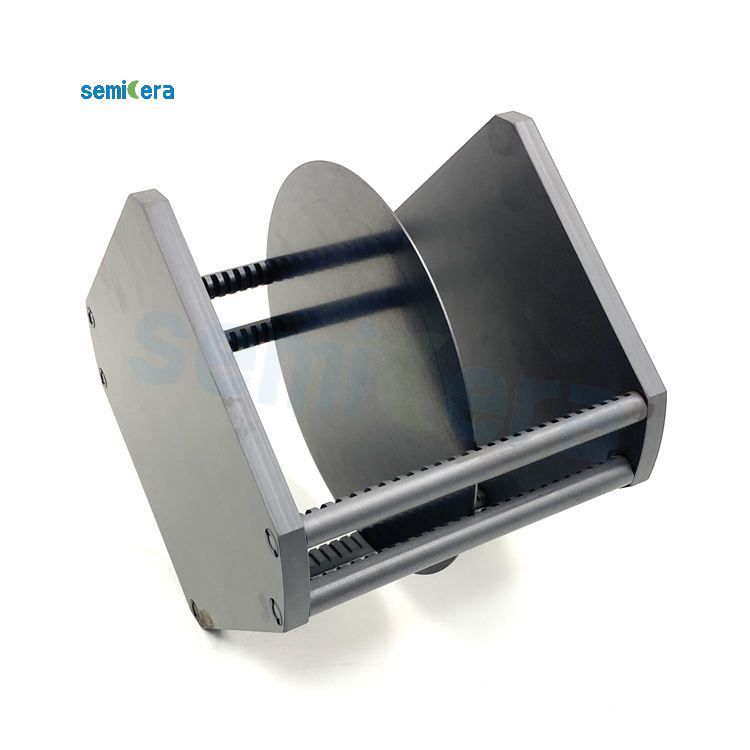

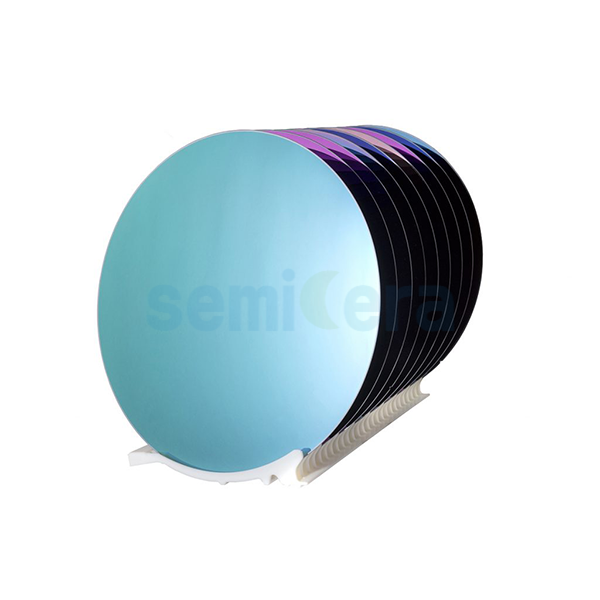

| An jeneral | Wafer Dyamèt | 50/75/100/125/150/200mm±25um |

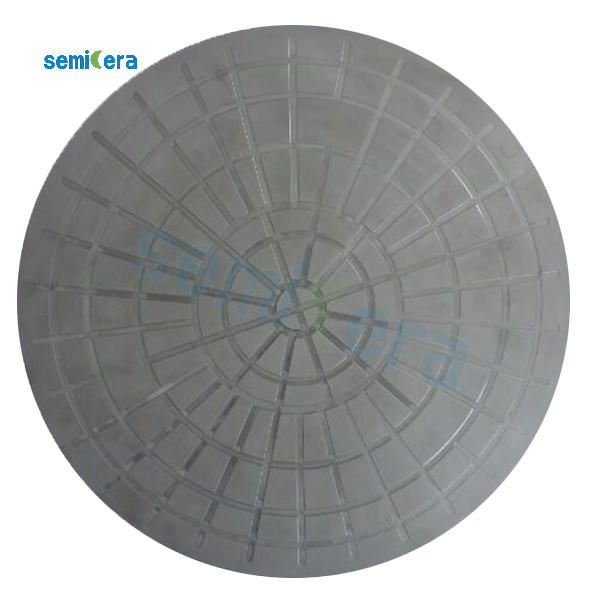

| Banza/Deformation | <10um | |

| Patikil | 0.3um <30ea | |

| Apatman/dan | Flat oswa Notch | |

| Eksklizyon Edge | / | |

| Kouch Aparèy | Aparèy-kouch Kalite/Dopant | N-Type/P-Type |

| Aparèy-kouch Oryantasyon | <1-0-0> / <1-1-1> / <1-1-0> | |

| Aparèy-kouch Epesè | 0.1 ~ 300um | |

| Aparèy-kouch rezistivite | 0.001 ~ 100,000 ohm-cm | |

| Aparèy-kouch Patikil | <30ea@0.3 | |

| Aparèy Kouch TTV | <10um | |

| Kouch Aparèy Fini | Poli | |

| BOX | Antre epesè oksid tèmik | 50nm (500Å) ~ 15um |

| Manch kouch | Manch Wafer Kalite / Dopant | N-Type/P-Type |

| Manch Wafer Oryantasyon | <1-0-0> / <1-1-1> / <1-1-0> | |

| Manch Wafer rezistivite | 0.001 ~ 100,000 ohm-cm | |

| Manch Wafer epesè | > 100um | |

| Manch Wafer Fini | Poli | |

| Kafe SOI nan espesifikasyon sib yo ka Customized selon kondisyon kliyan yo. | ||