1.Ou sikwi entegre

1.1 Konsèp ak nesans sikui entegre yo

Sikwi entegre (IC): refere a yon aparèy ki konbine aparèy aktif tankou tranzistò ak dyod ak konpozan pasif tankou rezistans ak kondansateur atravè yon seri de teknik pwosesis espesifik.

Yon kous oswa sistèm ki "entegre" sou yon semi-conducteurs (tankou Silisyòm oswa konpoze tankou galyòm arsenide) wafer dapre sèten entèkoneksyon sikwi ak Lè sa a, pake nan yon koki pou fè fonksyon espesifik.

An 1958, Jack Kilby, ki te responsab pou miniaturizasyon ekipman elektwonik nan Texas Instruments (TI), te pwopoze lide sikui entegre yo:

"Piske tout konpozan tankou kondansateur, rezistans, tranzistò, elatriye ka fèt nan yon sèl materyèl, mwen te panse li ta posib fè yo sou yon moso nan materyèl semi-conducteurs ak Lè sa a, konekte yo pou fòme yon kous konplè."

Sou 12 septanm ak 19 septanm 1958, Kilby te konplete fabrikasyon ak demonstrasyon osilator ak deklanche faz-chanjman an, respektivman, ki make nesans kous entegre a.

Nan lane 2000, Kilby te bay Pri Nobèl nan Fizik. Komite Pri Nobèl la te fè kòmantè yon fwa ke Kilby "tete fondasyon pou teknoloji enfòmasyon modèn."

Foto ki anba a montre Kilby ak patant sikwi entegre li a:

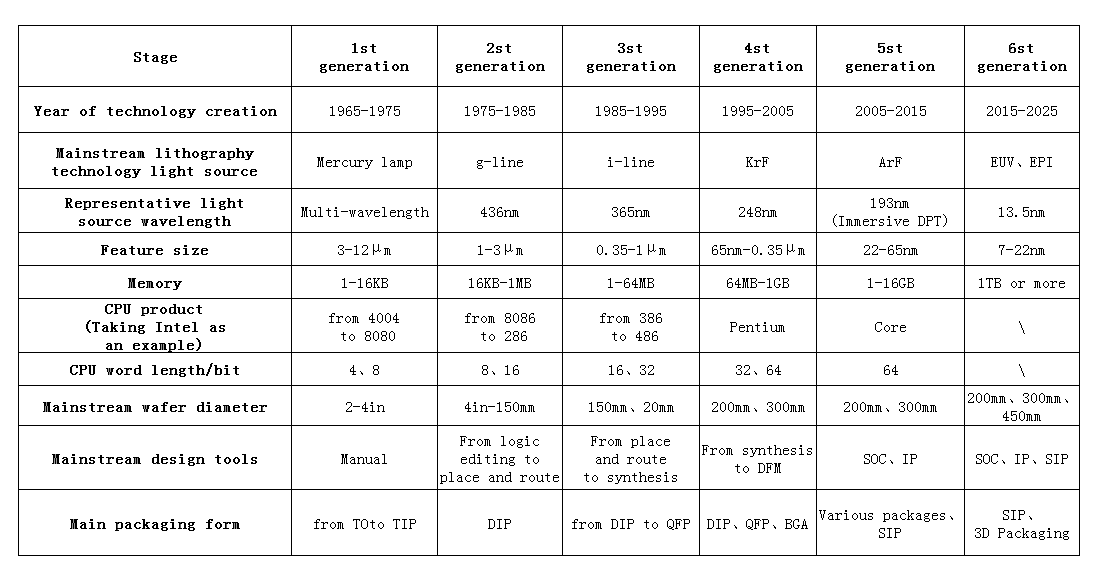

1.2 Devlopman teknoloji fabrikasyon semi-conducteurs

Figi sa a montre etap devlopman teknoloji fabrikasyon semi-conducteurs:

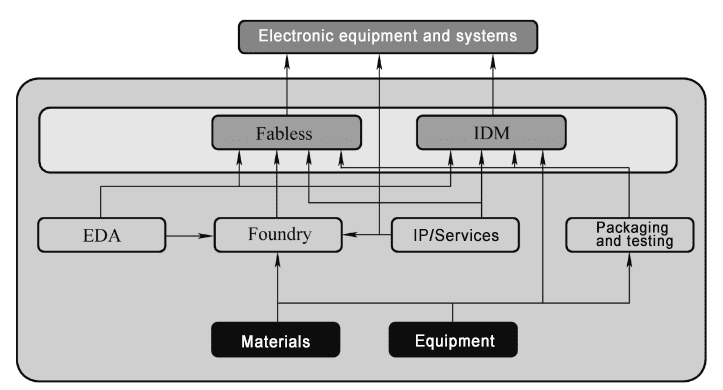

1.3 Integrated Circuit Industry Chain

Konpozisyon chèn endistri semi-conducteurs (sitou entegre, ki gen ladan aparèy disrè) yo montre nan figi ki anwo a:

- Fabless: Yon konpayi ki desine pwodwi san yon liy pwodiksyon.

- IDM: Manifakti aparèy entegre, manifakti aparèy entegre;

- IP: manifakti modil sikwi;

- EDA: Elektwonik Design Otomatik, automatisation konsepsyon elektwonik, konpayi an sitou bay zouti konsepsyon;

- Fonderie; Fondri wafer, bay sèvis fabrikasyon chip;

- Anbalaj ak tès konpayi fondri: sitou sèvi Fabless ak IDM;

- Materyèl ak konpayi ekipman espesyal: sitou bay materyèl ki nesesè yo ak ekipman pou konpayi fabrikasyon chip yo.

Pwodwi prensipal yo pwodwi lè l sèvi avèk teknoloji semi-conducteurs yo se sikui entegre ak aparèy semi-kondiktè disrè.

Pwodwi prensipal yo nan sikui entegre yo enkli:

- Pati Aplikasyon Espesifik Creole (ASSP);

- Mikwoprosesè Inite (MPU);

- Memwa

- Aplikasyon espesifik sikwi entegre (ASIC);

- Awondisman analòg;

- Sikwi lojik jeneral (Sikwi lojik).

Pwodwi prensipal yo nan aparèy disrè semi-conducteurs yo enkli:

- Dyòd;

- Tranzistò;

- Aparèy pouvwa;

- Aparèy High-Voltage;

- Aparèy mikwo ond;

- Optoelektwonik;

- Aparèy Capteur (Capteur).

2. Pwosesis manifakti sikwi entegre

2.1 Chip Faktori

Plizyè douzèn oswa menm dè dizèn de milye bato espesifik yo ka fèt ansanm sou yon wafer Silisyòm. Nimewo a nan chips sou yon wafer Silisyòm depann sou kalite a nan pwodwi ak gwosè a nan chak chip.

Silisyòm wafers yo dabitid rele substrats. Dyamèt Silisyòm gauf yo te ogmante pandan ane yo, depi mwens pase 1 pous nan kòmansman rive nan 12 pous yo souvan itilize (apeprè 300 mm) kounye a, epi li ap sibi yon tranzisyon nan 14 pous oswa 15 pous.

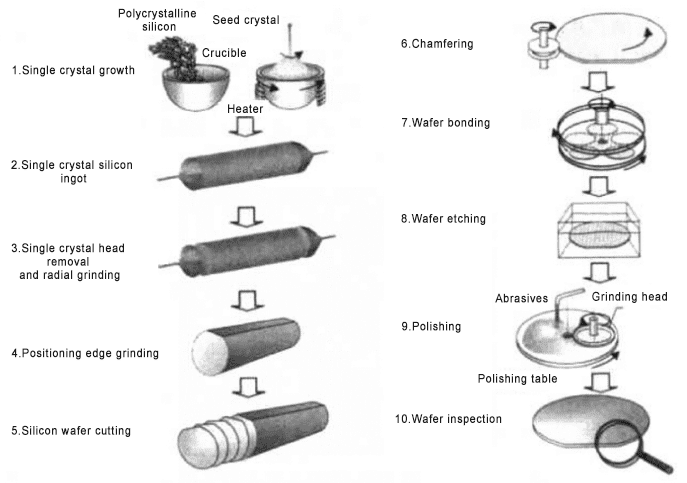

Manifakti chip jeneralman divize an senk etap: preparasyon wafer Silisyòm, fabrikasyon wafer Silisyòm, tès / davwa chip, asanble ak anbalaj, ak tès final la.

(1)

Silisyòm wafer preparasyon:

Pou fè materyèl la anvan tout koreksyon, Silisyòm ekstrè soti nan sab ak pirifye. Yon pwosesis espesyal pwodui lengote Silisyòm ki gen dyamèt apwopriye. Lè sa a, lengote yo koupe nan gauf Silisyòm mens pou fè microchips.

Wafers yo prepare nan espesifikasyon espesifik, tankou kondisyon rebò anrejistreman ak nivo kontaminasyon.

(2)Silisyòm wafer manifakti:

Epitou li te ye kòm manifakti chip, wafer nan Silisyòm fè rive nan plant fabrikasyon an Silisyòm ak Lè sa a, ale nan netwayaj divès kalite, fòmasyon fim, fotolitografi, grave ak etap dopaj. Wafer Silisyòm trete a gen yon seri konplè sikui entegre pèmanan grave sou wafer Silisyòm lan.

(3)Tès ak seleksyon wafers Silisyòm:

Apre manifakti silisyòm wafer fini, silisyòm wafers yo voye nan zòn tès / sòt, kote chips endividyèl yo sonde ak elektrik teste. Lè sa a, bato ki akseptab ak akseptab yo klase, epi yo make chips ki defektye.

(4)Asanble ak anbalaj:

Apre tès / klasman wafer, gaufre yo antre nan etap asanble ak anbalaj pou pake chips endividyèl yo nan yon pake tib pwoteksyon. Se bò dèyè wafer la tè pou diminye epesè substra a.

Yon fim plastik epè tache nan do a nan chak wafer, ak Lè sa a, yo itilize yon lam dyaman-pwent wè pou separe chips yo sou chak wafer sou liy yo ekri sou bò devan an.

Fim plastik ki sou do wafer Silisyòm lan anpeche chip Silisyòm lan tonbe. Nan plant asanble a, bon chips yo bourade oswa evakye pou fòme yon pake asanble. Apre sa, chip la sele nan yon koki plastik oswa seramik.

(5)Tès final la:

Pou asire fonksyonalite chip la, yo teste chak sikwi entegre pake pou satisfè kondisyon elektrik ak anviwònman karakteristik paramèt manifakti a. Apre tès final la, yo voye chip la bay kliyan an pou asanble nan yon kote devwe.

2.2 Divizyon Pwosesis

Pwosesis manifakti sikwi entegre yo jeneralman divize an:

Front-end: Pwosesis devan-fen an jeneralman refere a pwosesis fabrikasyon aparèy tankou tranzistò, sitou ki gen ladan pwosesis fòmasyon izolasyon, estrikti pòtay, sous ak drenaj, twou kontak, elatriye.

Back-end: Pwosesis back-end la sitou refere a fòmasyon nan liy entèkoneksyon ki ka transmèt siyal elektrik nan divès aparèy sou chip la, sitou ki gen ladan pwosesis tankou depo dielectric ant liy entèkoneksyon, fòmasyon liy metal, ak fòmasyon pad plon.

Mwayen etap: Yo nan lòd yo amelyore pèfòmans nan tranzistò, nœuds teknoloji avanse apre 45nm / 28nm itilize dielectrics pòtay segondè-k ak pwosesis pòtay metal, epi ajoute pwosesis pòtay ranplasman ak pwosesis entèkoneksyon lokal apre yo fin prepare sous tranzistò a ak estrikti drenaj. Pwosesis sa yo se ant pwosesis front-end la ak pwosesis back-end la, epi yo pa itilize nan pwosesis tradisyonèl yo, kidonk yo rele yo pwosesis mitan etap.

Anjeneral, pwosesis preparasyon twou kontak la se liy divize ant pwosesis la devan-fen ak pwosesis la back-end.

Kontakte twou: yon twou grave vètikal nan wafer Silisyòm pou konekte liy premye kouch metal entèkoneksyon an ak aparèy substra a. Li ranpli ak metal tankou tengstèn epi li itilize pou mennen elektwòd aparèy la nan kouch entèkoneksyon metal la.

Atravè twou: Li se chemen an koneksyon ant de kouch adjasan nan liy entèkonekte metal, ki chita nan kouch nan dyelèktrik ant de kouch metal yo, epi li jeneralman plen ak metal tankou kwiv.

Nan yon sans laj:

Pwosesis Front-end: Nan yon sans laj, manifakti sikwi entegre ta dwe gen ladan tou tès, anbalaj ak lòt etap. Konpare ak tès ak anbalaj, eleman ak fabrikasyon entèkonekte yo se premye pati nan manifakti sikwi entegre, kolektivman refere yo kòm pwosesis front-end;

Pwosesis back-end: Tès ak anbalaj yo rele pwosesis back-end.

3. Apendis

SMIF: Entèfas mekanik estanda

AMHS: Sistèm Otomatik Transmisyon Materyèl

OHT: transfè anlè anlè

FOUP: Ouvèti devan inifye Pod, eksklizif pou 12 pous (300mm)

Sa ki pi enpòtan,Semicera ka baypati grafit, mou/rijid te santi,pati carbure Silisyòm, Pati carbure Silisyòm CVD, akSiC/TaC kouvwi patiak pwosesis semi-conducteurs konplè nan 30 jou.Nou sensèman gade pou pi devan pou vin patnè alontèm ou nan Lachin.

Tan pòs: Out-15-2024