Apèsi sou Pwosesis Semiconductor

Pwosesis semi-conducteurs prensipalman enplike nan aplikasyon mikrofabrikasyon ak teknoloji fim pou konekte konplètman chips ak lòt eleman nan divès rejyon, tankou substrats ak ankadreman. Sa a fasilite ekstraksyon nan tèminal plon ak ankapsulasyon ak yon mwayen izolasyon plastik yo fòme yon antye entegre, prezante kòm yon estrikti ki genyen twa dimansyon, finalman ranpli pwosesis la anbalaj semi-conducteurs. Konsèp nan pwosesis semi-conducteurs tou gen rapò ak definisyon an etwat nan anbalaj chip semi-conducteurs. Soti nan yon pèspektiv pi laj, li refere a jeni anbalaj, ki enplike konekte ak fikse nan substra a, konfigirasyon ekipman elektwonik ki koresponn lan, ak konstwi yon sistèm konplè ak gwo pèfòmans konplè.

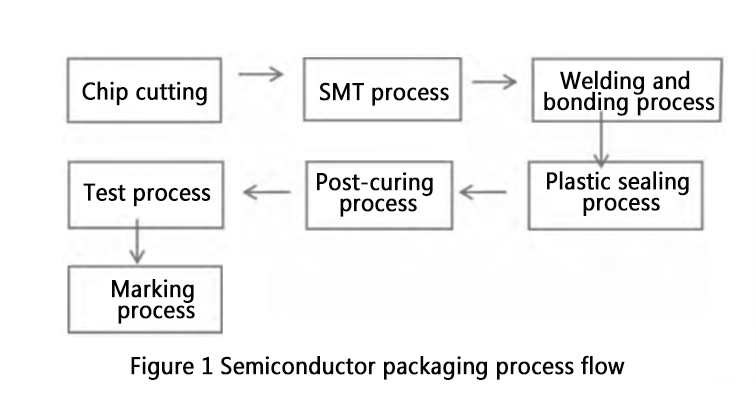

Semiconductor anbalaj pwosesis koule

Pwosesis anbalaj semi-kondiktè a gen ladan travay miltip, jan sa montre nan Figi 1. Chak pwosesis gen kondisyon espesifik ak workflows ki gen rapò sere, ki nesesè analiz detaye pandan etap pratik la. Kontni espesifik la se jan sa a:

1. Chip Koupe

Nan pwosesis anbalaj semi-conducteurs, koupe chip enplike tranche Silisyòm wafers nan chips endividyèl ak san pèdi tan retire debri Silisyòm pou anpeche antrav nan travay ki vin apre ak kontwòl kalite.

2. Chip Mounting

Pwosesis aliye chip la konsantre sou evite domaj sikwi pandan fanm k'ap pile wafer pa aplike yon kouch fim pwoteksyon, toujou mete aksan sou entegrite sikwi.

3. Pwosesis Liaison Fil

Kontwole bon jan kalite a nan pwosesis la lyezon fil enplike itilize diferan kalite fil lò konekte kousinen lyezon chip la ak kousinen ankadreman yo, asire chip la ka konekte nan sikui ekstèn epi kenbe entegrite pwosesis an jeneral. Tipikman, yo itilize fil lò dope ak fil lò alyaj.

Doped Fil lò: Kalite yo enkli GS, GW, ak TS, apwopriye pou arc segondè (GS: > 250 μm), arc mwayen-segondè (GW: 200-300 μm), ak arc mwayen-ba (TS: 100-200). μm) lyezon respektivman.

Fil lò alyaj: Kalite yo enkli AG2 ak AG3, apwopriye pou lyezon ba-ark (70-100 μm).

Opsyon dyamèt pou fil sa yo varye ant 0.013 mm ak 0.070 mm. Chwazi kalite ki apwopriye ak dyamèt ki baze sou kondisyon operasyonèl ak estanda enpòtan anpil pou kontwòl kalite.

4. Pwosesis bòdi

Sikwi prensipal la nan eleman bòdi enplike enkapsulasyon. Kontwole bon jan kalite a nan pwosesis la bòdi pwoteje eleman yo, espesyalman soti nan fòs ekstèn ki lakòz diferan degre nan domaj. Sa a enplike bon jan analiz de pwopriyete fizik eleman yo.

Twa metòd prensipal yo itilize kounye a: anbalaj seramik, anbalaj plastik, ak anbalaj tradisyonèl yo. Jere pwopòsyon chak kalite anbalaj enpòtan anpil pou satisfè demand pwodiksyon chip mondyal yo. Pandan pwosesis la, kapasite konplè yo nesesè, tankou prechofe chip la ak ankadreman plon anvan ankapsulasyon ak résine epoksidik, bòdi, ak geri apre mwazi.

5. Pwosesis apre-geri

Apre pwosesis la bòdi, tretman apre-geri nesesè, konsantre sou retire nenpòt materyèl depase alantou pwosesis la oswa pake. Kontwòl kalite esansyèl pou evite afekte kalite pwosesis jeneral ak aparans.

6.Tès Pwosesis

Yon fwa pwosesis anvan yo fini, bon jan kalite jeneral pwosesis la dwe teste lè l sèvi avèk teknoloji ak enstalasyon tès avanse. Etap sa a enplike nan anrejistreman detaye nan done, konsantre sou si chip la opere nòmalman ki baze sou nivo pèfòmans li yo. Etandone pri a wo nan ekipman tès, li enpòtan pou kenbe kontwòl kalite pandan tout etap pwodiksyon yo, ki gen ladan enspeksyon vizyèl ak tès pèfòmans elektrik.

Tès Pèfòmans Elèktrik: Sa a enplike nan tès sikui entegre lè l sèvi avèk ekipman tès otomatik epi asire chak sikwi byen konekte pou tès elektrik.

Enspeksyon vizyèl: Teknisyen yo sèvi ak mikwoskòp pou byen enspekte chips yo pake fini pou asire yo pa gen defo ak satisfè estanda kalite anbalaj semi-conducteurs.

7. Marking Pwosesis

Pwosesis maketing la enplike transfere chips yo teste nan yon depo semi-fini pou pwosesis final la, enspeksyon kalite, anbalaj, ak anbake. Pwosesis sa a gen ladan twa etap prensipal:

1) Electroplating: Apre fòme fil yo, yo aplike yon materyèl anti-korozyon pou anpeche oksidasyon ak korozyon. Teknoloji depo galvanoplastie tipikman itilize paske pifò kondwi yo fèt ak fèblan.

2) Koube: Lè sa a, kondwi yo trete yo gen fòm, ak teren an sikwi entegre mete nan yon zouti ki fòme plon, kontwole fòm nan plon (J oswa L kalite) ak anbalaj sifas-monte.

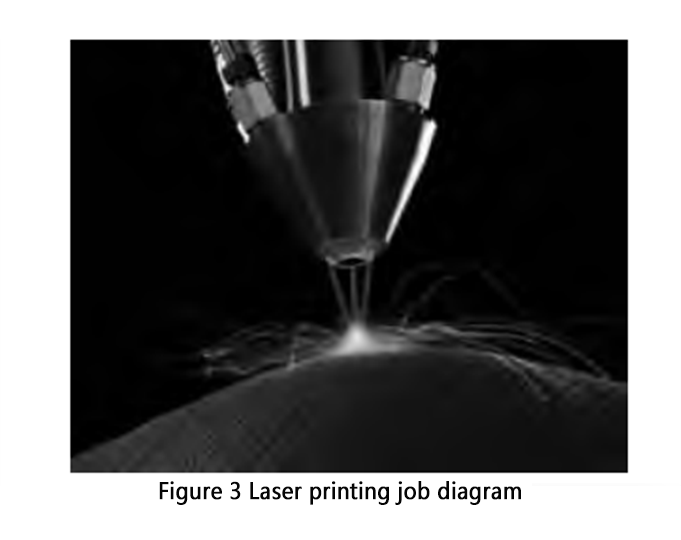

3) Enpresyon lazè: Finalman, pwodwi yo fòme yo enprime ak yon konsepsyon, ki sèvi kòm yon mak espesyal pou pwosesis anbalaj semi-conducteurs, jan sa montre nan Figi 3.

Defi ak Rekòmandasyon

Etid la nan pwosesis anbalaj semi-conducteurs kòmanse ak yon BECA de teknoloji semi-conducteurs yo konprann prensip li yo. Apre sa, egzamine koule pwosesis anbalaj la gen pou objaktif pou asire kontwòl metikuleu pandan operasyon yo, lè l sèvi avèk jesyon rafine pou fè pou evite pwoblèm woutin. Nan kontèks devlopman modèn, idantifye defi nan pwosesis anbalaj semi-conducteurs esansyèl. Li rekòmande yo konsantre sou aspè kontwòl kalite, byen metrize pwen kle yo efektivman amelyore kalite pwosesis la.

Analize nan yon pèspektiv kontwòl kalite, gen defi enpòtan pandan aplikasyon akòz pwosesis anpil ak kontni espesifik ak kondisyon, chak enfliyanse lòt la. Kontwòl rijid nesesè pandan operasyon pratik. Lè w adopte yon atitid travay metikuleu ak aplike teknoloji avanse, bon jan kalite pwosesis anbalaj semi-conducteurs ak nivo teknik yo ka amelyore, asire efikasite aplikasyon konplè ak reyalize ekselan benefis jeneral. (jan yo montre nan Figi 3).

Lè poste: Me-22-2024